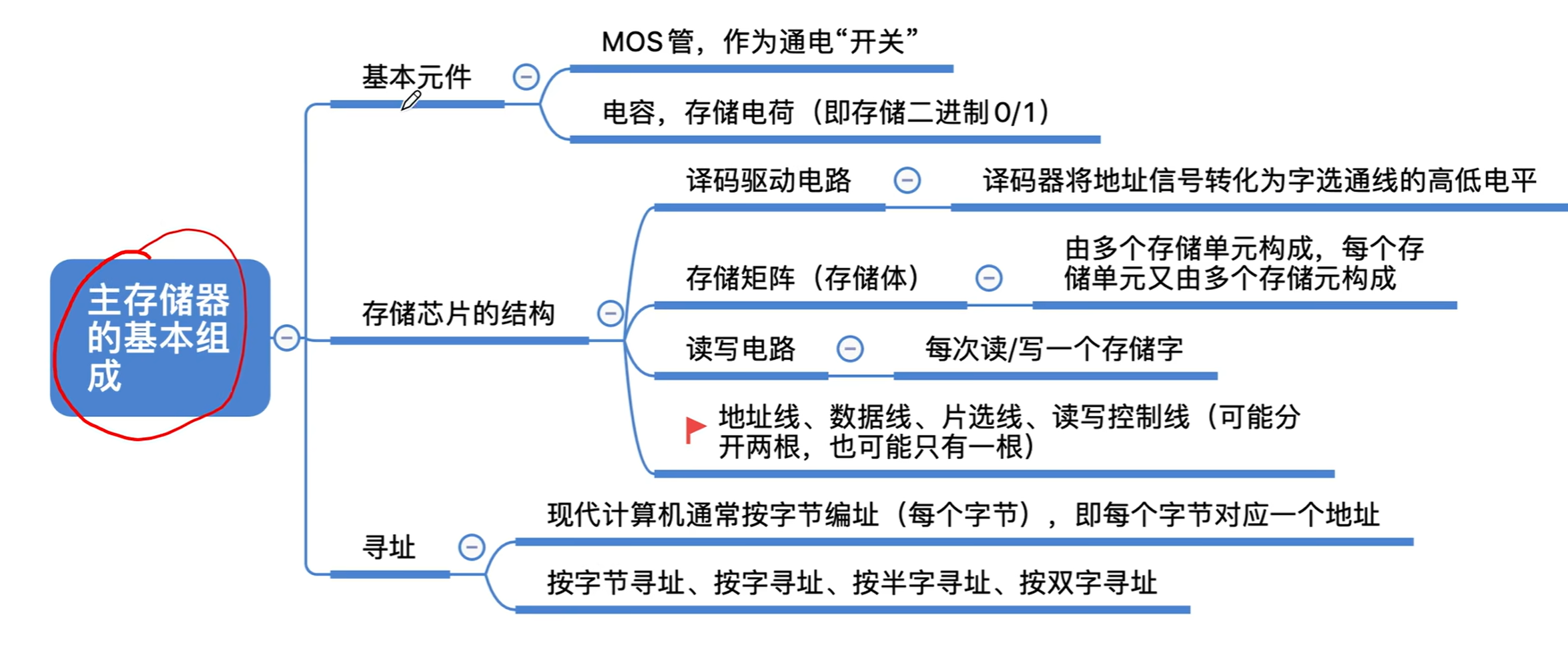

- 主存储器的基本组成

- 半导体元件的原理

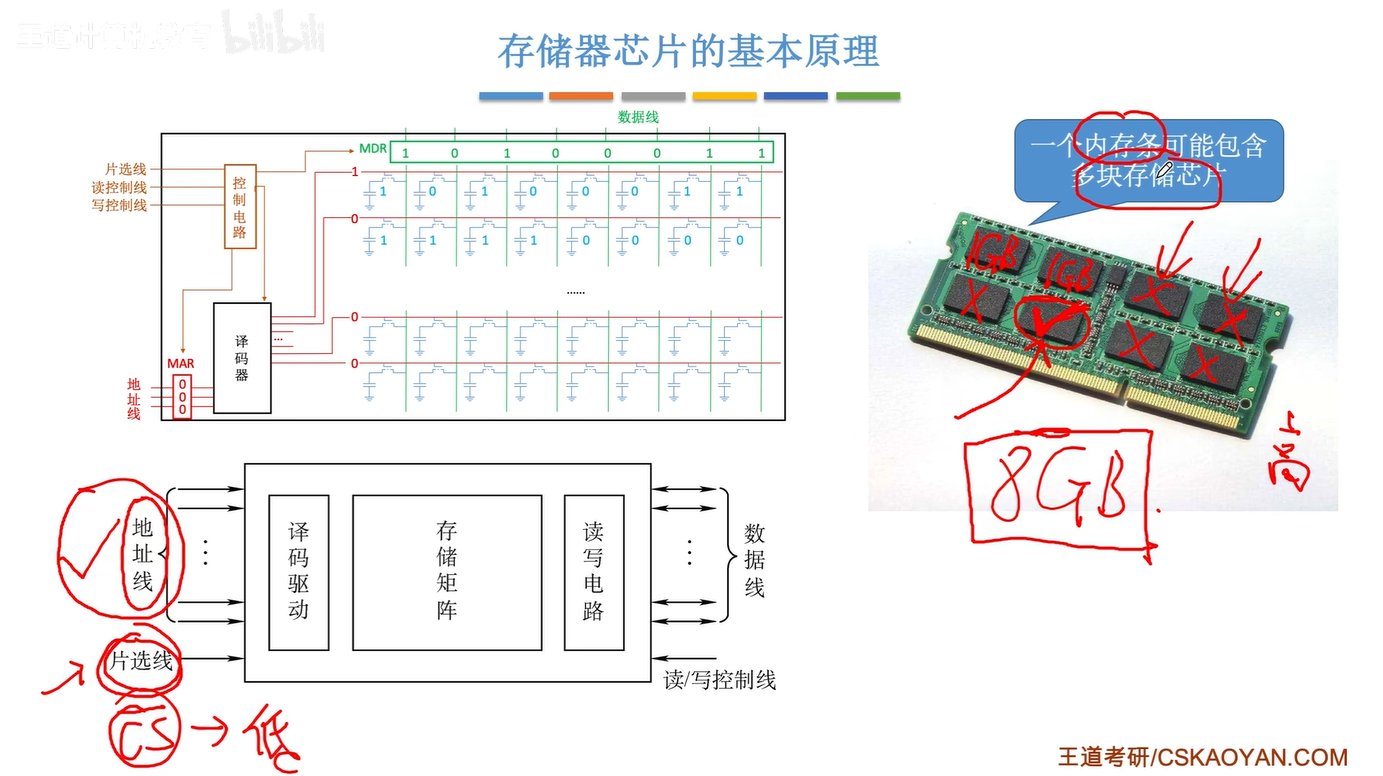

- 存储芯片的基本原理

- 如何实现不同的寻址方式

基本的半导体元件的原理

读写二进制的原理

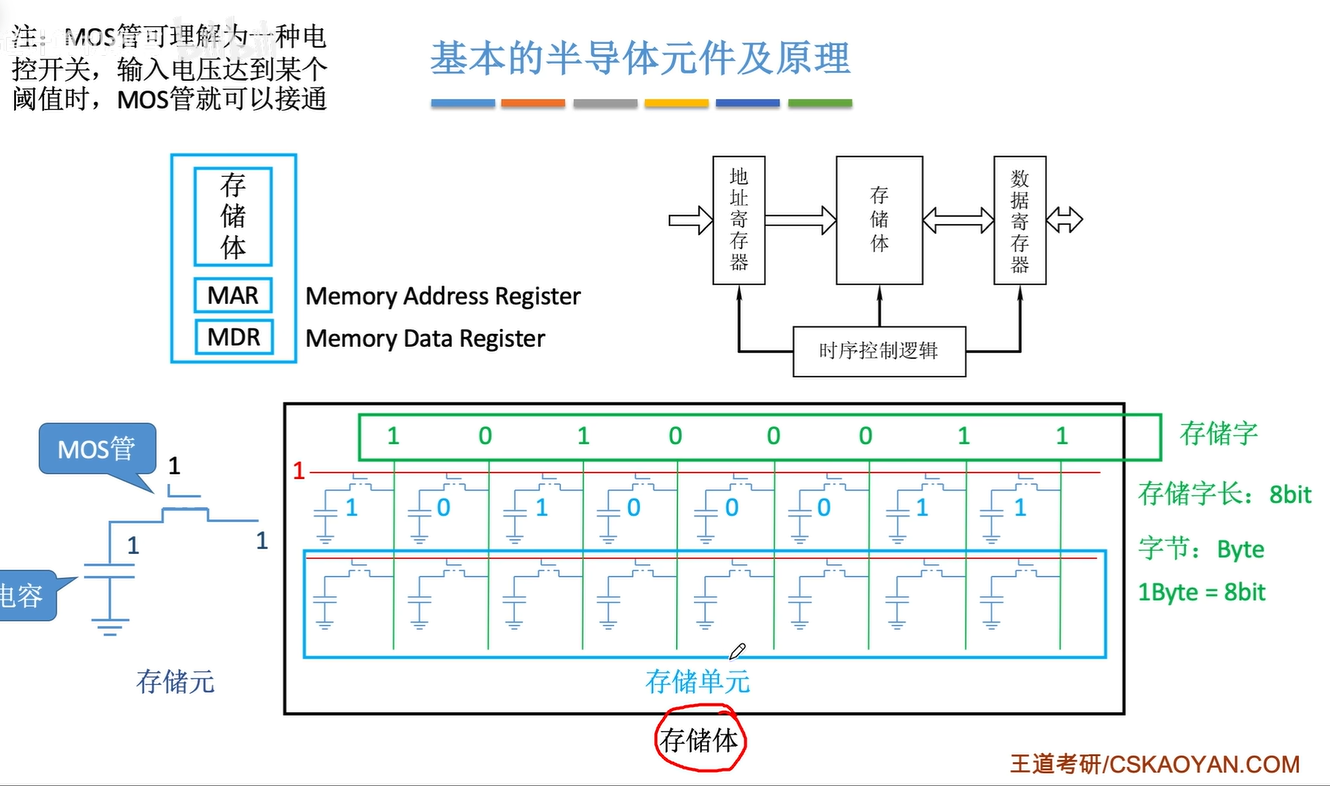

在第一章我们说过一个主存储器,逻辑上可以分为三部分:

-

存储体

-

MAR(地址存储器)

-

MDR(数据存储器)

这三个部件会在时序控制逻辑下有条不紊地相互配合着工作。

NOTE一个存储体由多个存储元构成。

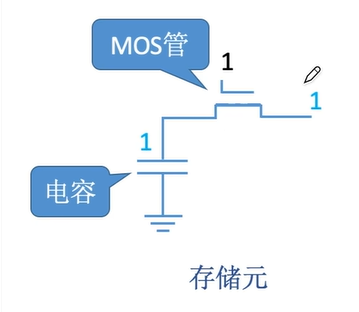

为什么叫作半导体元件?因为不是导体,也不是绝缘体。在满足一定的电压条件下,这个绝缘体可以变成导体。

MOS管就是一种典型的半导体元件。输出电压(或可理解为高电平信号的1),电容内的电荷就会顺着导线往外流,最终在导线端检测到信号(无信号则说明存储的是0)。

这便是读出一个二进制的原理,需要用到一个MOS管和一个电容 。

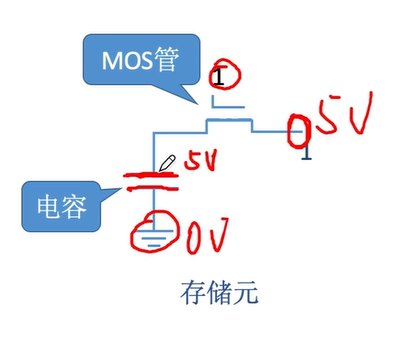

再来看写入一个二进制的原理。

我们从导线端加一个5V的高电平,同时给MOS管也加一个5V的高电平。

接通之后,意味着电容上端也有了5V的电压。而下边这个金属板由于是接地,所以是0V。那只要电容的两块金属板之间有了这种电压差,就会导致电容内电荷开始移动,于是这个电容就会存储一些电荷,也就是存储了二进制的1。

接下来我们再让这个MOS管断开,这样电容里的电荷是不是就跑不出去了。

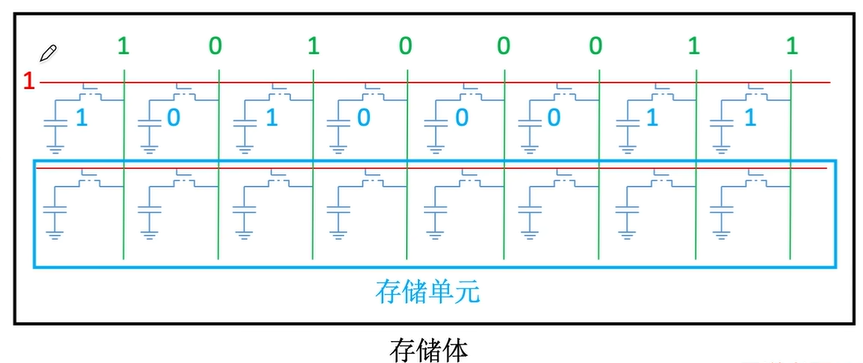

存储单元和存储体

如果我们把多个存储元进行科学合理的连接,那么我们就一次性读出或写入多个二进制的数据。

比如说现在上面这一排存储元,他们存储的二进制信息分别是这样的一些值。

1,0,1,0,0,0,1,1

注意这张图里有一条红色的线,连接了每一个存储元的MOS管。如果给这条线加一个5V的高电平,意味着所有的MOS管都可以导通。

导通之后,电容里存储的电荷就可以顺着这条线从绿色的线往外导出。

也就是说,我们只需要检测绿色的线,就可以判断每一条线所对应的是0还是1,如果有电流,意味着是1,无电流则是0。

那么这样的一整行,就是所谓的存储单元,也就是一个存储字。

而多个存储单元就构造成了存储体,又叫存储矩阵。

那么我们一次可以读出的这些二进制位就是一个存储字。

在这个例子中,存储字长为8bit,因为一行总共有8个存储元。显然对于由n个存储元的存储单元构成的存储体,存储字长为n bit。

由于接的MOS管都是一根线,如果要接通,那么8个存储单元会一并被接通,也就可以同时被读出或者写入。

请再次注意,字节和存储字的区别。

NOTE一个字节(Byte)必定有1Byte = 8bit,而一个存储字等于多少个比特,具体得看存储体的结构。

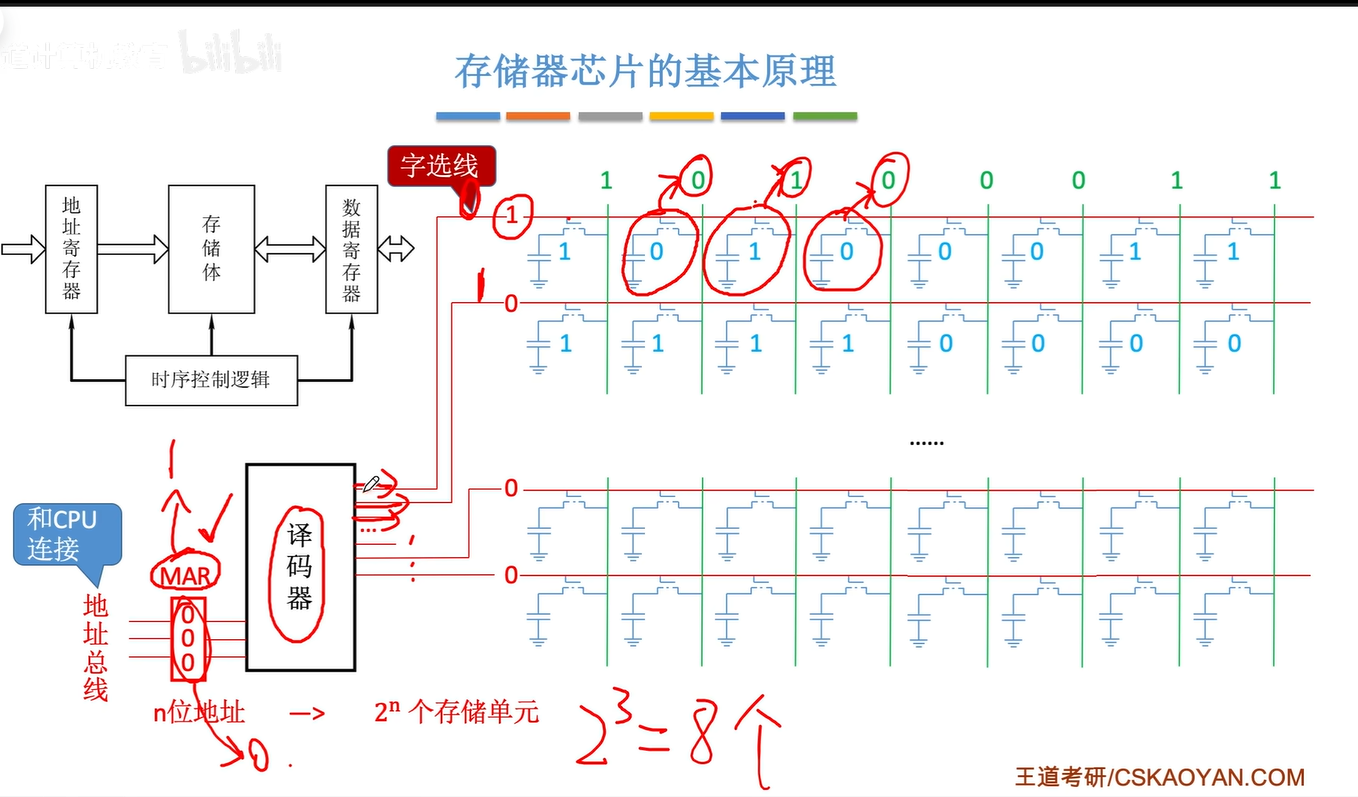

存储器芯片的基本原理

译码器

如何根据地址来决定我们要读或者要写哪个存储字呢?

这涉及到译码器的使用。

译码器的作用:在给出n个地址后,这些地址会对应2^n个存储单元。译码器会根据地址寄存器MAR里给出的这些地址,把它们转变成某一条选通线的高电平信号。

比如,此时CPU给MAR送过来的地址的3个0,翻译成十进制对应十进制的0。

那么译码器会把第0根字选择线给一个高电平的输出,这样第一个存储字所对应的存储元件都会被选通,就可以读出和写入数据了。

总之,每一个地址会对应译码器的一条输出线,0号,1号,2号…以此类推。总共有2^3个地址,也就是8个地址,因此译码器的输出端总共会有八条线。

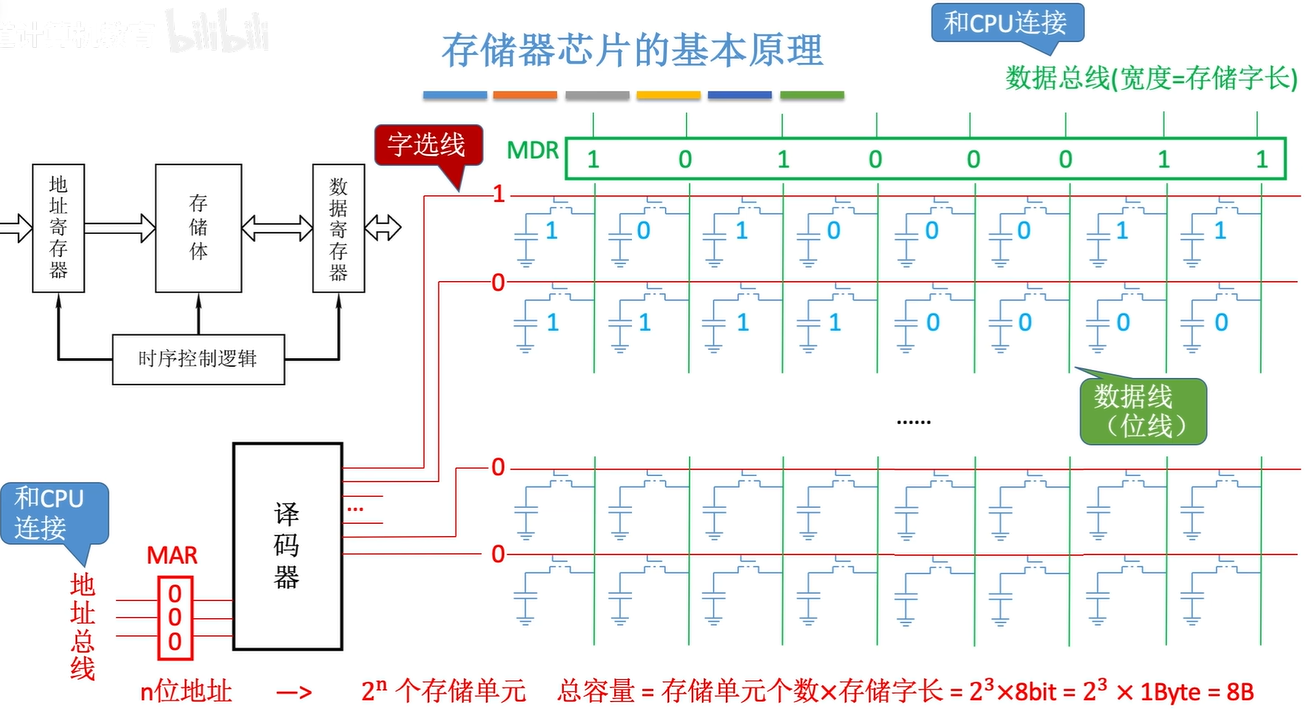

经过译码器的处理,一个地址信号会被转化成译码器的某一条输出线的高电平信号,再通过数据线(位线)把每一位的二进制信息传送到MDR当中。接下来CPU会通过数据总线,从MDR当中取走这一整个字的数据。

数据总线(宽度 = 存储字长) 存储体总容量 = 存储单元个数 * 存储字长

这就是给出地址之后通过译码器选中某一个字的原理。

控制电路

继续完善这个存储芯片的构成,增加一个控制电路,用于控制译码器MAR和MDR。

比如,CPU通过地址总线把地址送到MAR当中,但是由于我们使用的是电信号来传送这些二进制数据,而电信号难免会有不稳定的情况。因此当MAR里面的这个电信号稳定之前,这个地址信息是不能送到译码器当中的。

这就是控制电路的一个作用,只有MAR稳定之后,它才会打开译码器的开关,让译码器来翻译这个地址,然后给出相应的输出信号。

同样的,当数据输出的时候,只有输出的电信号稳定之后,控制电路才会认为此时的输出是正确无误的。所以它也要控制MDR在什么时候给数据总线送出数据。

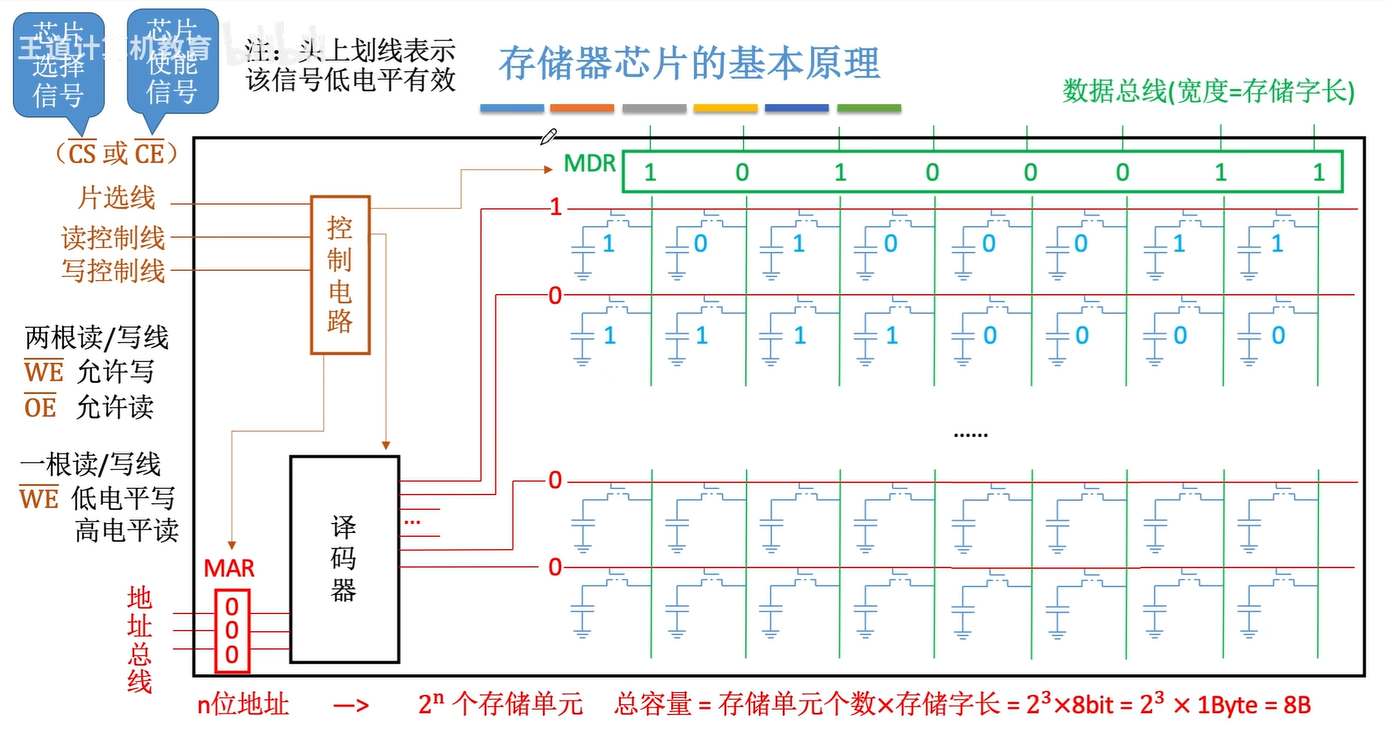

片选线

另一方面,存储芯片还需要对外提供一些线路,一个叫片选线,通常用CS(Chip Select,芯片选择信号)或CE(Chip Enable,芯片使能信号)上面加一个杠来表示片选线的电信号。

头上划杠的意思,就是当这个电信号是低电平的时候有效。

当给出低电平的时候,就说明这个芯片的总开关是被我们接通的,也就是可以工作的。

读写控制线

除了片选线,控制电路还需要对外提供读控制线和写控制线,有的地方也会把读控制线分成两条线。

WE的意思是允许写,上面画一条横杠的意思就是说当这个写控制线的信号WE是低电平的时候,表示此时这个芯片正在进行的是写操作,也就是要把MDR里保存的这些数据输入到各个电容当中。

同样的,当需要读出数据的时候,给读控制线OE电信号,让它变为低电平,控制电路就知道我们要进行一个读操作,而不是一个写操作了。

这是第一种设计方法。 还有一种常见的设计方法是可以把读写控制线合二为一,用一根线来表示此时要写还是读。

这种情况下,当输入一个低电平,表示写,输入一个高电平,表示读。

NOTE在题目当中会给出具体是哪一种设计方法。 当采用不同的设计方法,芯片的引脚数目也是不同的。

那么到目前为止,我们就得到了一块存储芯片的完整构造。

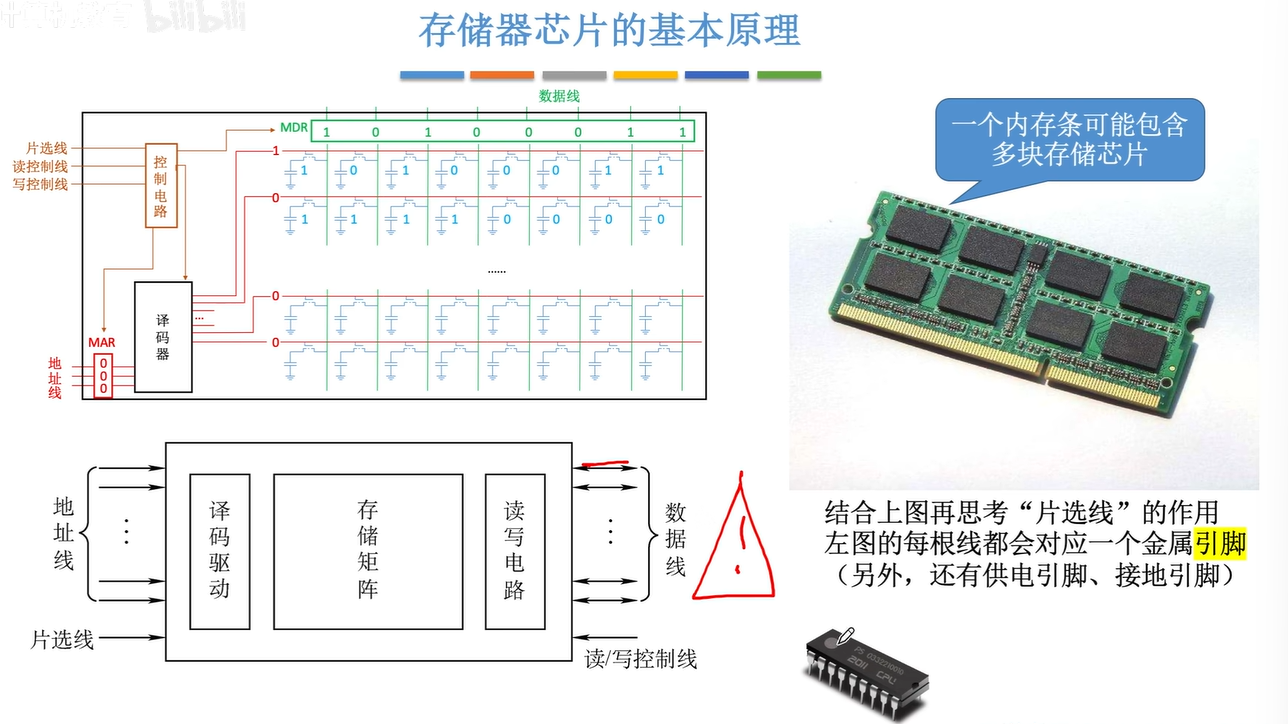

封装

把内部细节屏蔽掉,进行封装,那么逻辑上可以把存储器芯片的内部分成三大部分:

-

存储矩阵

-

译码驱动

-

读写电路

译码驱动包括译码器和驱动器,译码器上文已提及,驱动器的作用是把电信号放大,保证译码器输出的高电平信号稳定,有效,可靠。

读写线路包括了上文给出的红色,绿色的线还有控制电路。

比如,内存条中的黑色块状,其实就是一个个存储芯片。

当只想读取存储芯片的指定地址的数据,就需要让这块存储芯片的片选线信号有效(也就是CS给一个低电平),而其他电选线的信号都给一个高电平,这就是片选线的作用。

补充,每一块存储芯片都会暴露出金属引脚,用来接收地址信号等。常考根据芯片的参数信息判断芯片的引脚数目至少应该是多少,请根据以下方法判断:

-

每个地址线对应一个引脚。

-

每个数据线对应一个引脚。

-

片选线对应一个引脚。

-

读写控制线对应一个或两个引脚。

-

题目给出的供电引脚,接地引脚等。

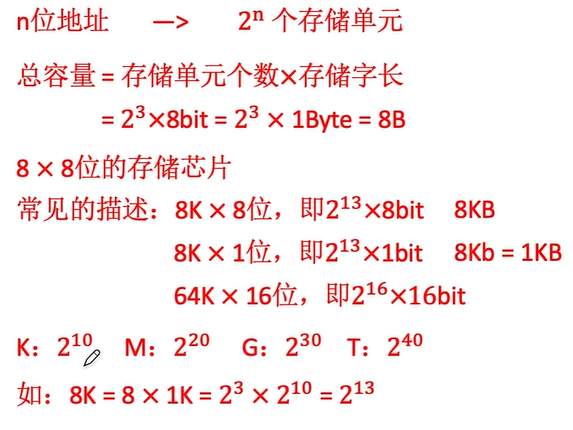

若给出n位地址,地址线需要有n条,对应2^n个存储单元,再根据公式:芯片总容量=存储单元个数x存储字长,乘上存储字长。

另外,一块存储芯片需要通地址线接受来自外界的地址信息(通常由CPU从地址总线传过来),还需要通过数据线进行数据的传输,除此之外,还需要片选线的电信号来确定这块芯片此时是否可用,也需要提供读写控制线(可能为1条或2条)

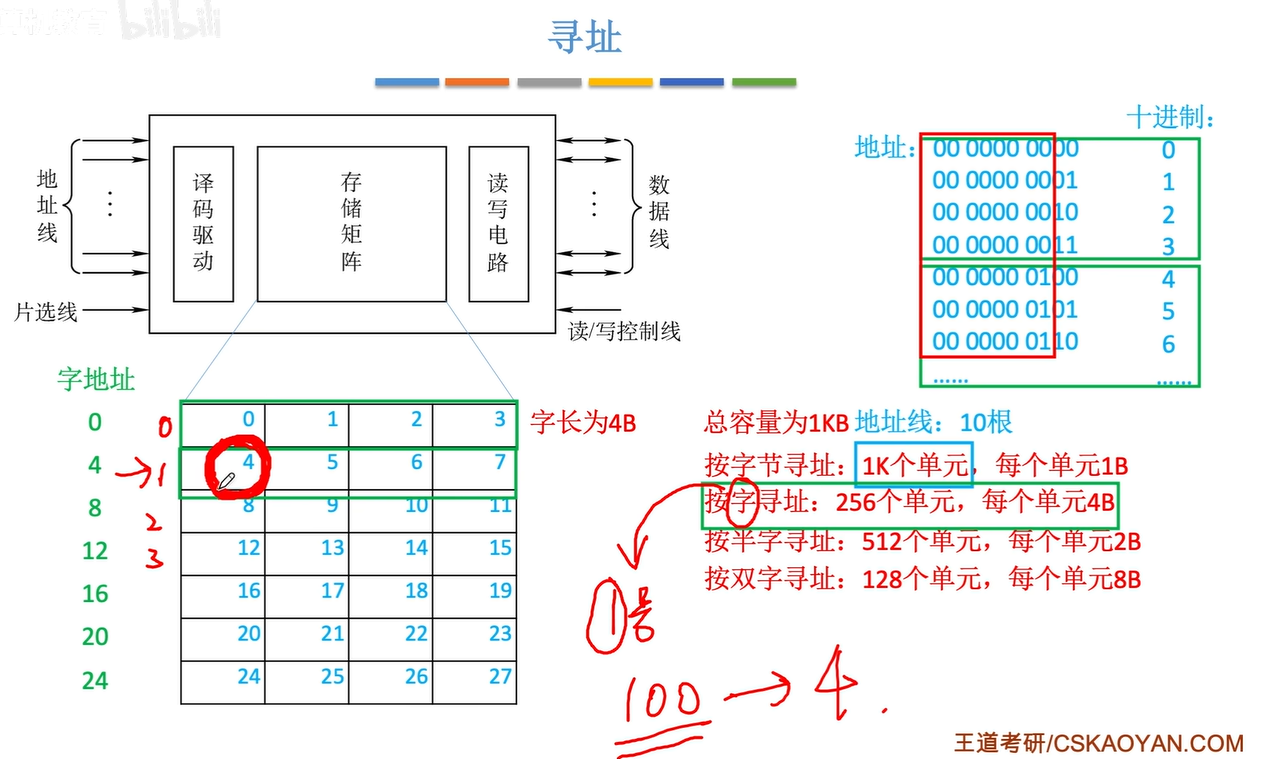

寻址

在图中,一个小方格表示一个字节(8bit)的信息,一行为一个存储字,也就是说这块存储芯片它的字长是4个字节。

假设总容量是1K个字节,i.e. 256个字,共256行。

每个字节会对应一个地址,共对应1k个地址。

那么地址线就应该有10根,因为2^10 = 1KB.

那么地址的二进制就应该从00 0000 0000 → 11 1111 1111,i.e. 0→1023.

若我们希望按字寻址,由于1个字占4个字节,因此把4个字节的地址合并,看作是1个字。当指明读的具体是哪个字的时候,只需要把字地址进行算术左移两位,就可以把字地址转换成与之对应的字节地址。

比如读1号字,也就是第二行的这个字1,将其二进制算术左移两位,也就是在末尾添2个0,得到100,对应十进制应该是4.

那么我们就得到了1号字的起始字节的地址。

按字节寻址,按半字寻址和按双字寻址也是类似原理。

知识回顾